Are you sure you want to delete this task? Once this task is deleted, it cannot be recovered.

|

|

1 year ago | |

|---|---|---|

| doc | 1 year ago | |

| planner | 1 year ago | |

| weaver | 1 year ago | |

| README.md | 2 years ago | |

| edif2blif.patch | 2 years ago | |

| rapidSmith.patch | 2 years ago | |

| vtr.patch | 2 years ago | |

README.md

PinTu目录结构:

.PinTu

├── readme.txt

├── doc

│ ├── Future Architecture_何安平.jpg

│ ├── PinTu_envConfig_温立_魏杰_康佳和_何安平.pdf

│ ├── PinTu_左翌_温立_魏杰_郁严贵_何安平.pdf

│ ├── v3_xdl文件生成_郁严贵_何安平.pdf

│ ├── 基于Xilinx FPGA的异步设计工具链研究_左翌.pdf

│ └── 介绍视频_郁严贵_何安平.mp4

├── hammer

│ ├── blifpretreat

│ │ ├── counter_new_auto.blif

│ │ ├── counter_new.blif

│ │ ├── counter_new.buf_tab

│ │ └── src

│ ├── edif2blif.patch

│ ├── edifpretreat

│ │ ├── counter.edif

│ │ ├── counter_new.edif

│ │ ├── src

│ │ └── tab

│ └── tabgenerate

│ ├── counter_new.buf_tab

│ ├── counter_new.edif

│ ├── counter_new.tab

│ └── src

├── iron

├── planner

│ ├── vtr.patch

│ └── vtr.sh

├── timer

├── weaver

│ ├── rapidSmith.patch

│ └── rapidSmith.sh

└── welder

doc: 关于整个项目的介绍、使用视频以及未来计划

hammer: 从edif格式文件到xdl文件的生成过程

planner:vtr的patch

weaver:rapidSmith的patch

准备工作:

下载源代码并打patch:

从https://codeload.github.com/verilog-to-routing/vtr-verilog-to-routing/zip/vpr_v5.0.2 下载vpr_v5.0.2解压得到vtr_release(文件名修改为vtr_release),复制vtr_release到planner目录下,在终端执行./vtr.sh命令。

从https://codeload.github.com/eddiehung/rapidSmith/zip/master 下载解压得到rapidSmith-master(文件名要修改为rapidSmith-master),复制rapidSmith-master到weaver目录下,在终端执行./rapidSmith.sh命令。

将上面得到的rapidSmith复制到vtr_release目录下,并将vtr_release复制到hammer目录下,最终vtr_release目录如下:

.vtr_release

├── abc_with_bb_support

├── bitstream

├── bitstream_1

├── bitstream_plus

├── libvpr

├── Makefile

├── ODIN_II

├── quick_test

├── rapidSmith

├── README.txt

├── run_quick_test.pl

├── vpr

├── vtr_flow

└── vtr-to-bitstream_v1.1.patch

从https://www.eecg.utoronto.ca/~jayar/software/edif2blif/edif2blif.html 下载解压得到edif2blif文件夹,并复制到hammer文件夹里,进入edif2blif目录后,

执行命令patch -p1 <../edif2blif.patch,最终的edif2blif目录如下:

.edif2blif

├── doc

├── scripts

├── src

├── tab

├── CONTENTS

├── counter_new.blif

├── counter_new.edif

└── README

环境配置:

PinTu的环境配置和可能遇到的问题在doc/PinTu_envConfig_温立_魏杰_康佳和_何安平.pdf下有详细说明。

hammer:

.

├── blifpretreat

│ ├── counter_new_auto.blif

│ ├── counter_new.blif

│ ├── counter_new.buf_tab

│ └── src

├── edif2blif

│ ├── doc

│ ├── scripts

│ ├── src

│ ├── tab

│ ├── CONTENTS

│ ├── counter_new.blif

│ ├── counter_new.edif

│ └── README

├── edifpretreat

│ ├── counter.edif

│ ├── counter_new.edif

│ ├── src

│ └── tab

├── tabgenerate

│ ├── counter_new.buf_tab

│ ├── counter_new.edif

│ ├── counter_new.tab

│ └── src

└── vtr_release

├── abc_with_bb_support

├── bitstream

├── bitstream_1

├── bitstream_plus

├── libvpr

├── Makefile

├── ODIN_II

├── quick_test

├── rapidSmith

├── README.txt

├── run_quick_test.pl

├── vpr

├── vtr_flow

└── vtr-to-bitstream_v1.1.patch

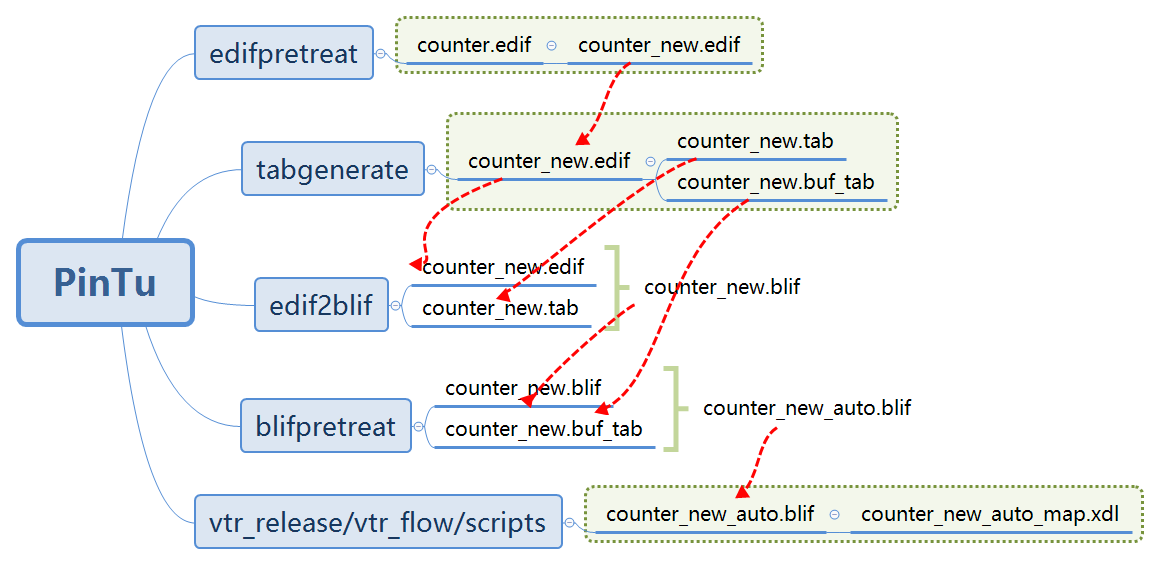

hammer执行流程(以counter.edif为例,给出每个步骤所需要的源文件和生成的文件),具体介绍参见doc目录中的内容:

郁严贵、康佳和

兰州大学异步电路与系统实验室

PinTu电子设计自动化(EDA)软件,是国际上最早的面向BBD型自定时型异步电路的EDA工具链。此工具提供了丰富的异步微流水线模版和全异步算子模块,使用者采用Verilog HDL并结合模版可设计出RTL级异步电路。此工具针对异步设计进行综合、延迟匹配与时序验证和仿真功能,完成从RTL级到门级工艺网表的综合,提供面向FPGA的布图和比特流生成功能,以及商用EDA的接口。

Diff